SK海力士正在与英伟达和其他逻辑设计商合作进行HBM4集成

SK海力士和英伟达正在对GPU进行彻底的重新设计,将HBM内存直接3D堆叠在处理核心之上。

(图片来源:SK海力士)

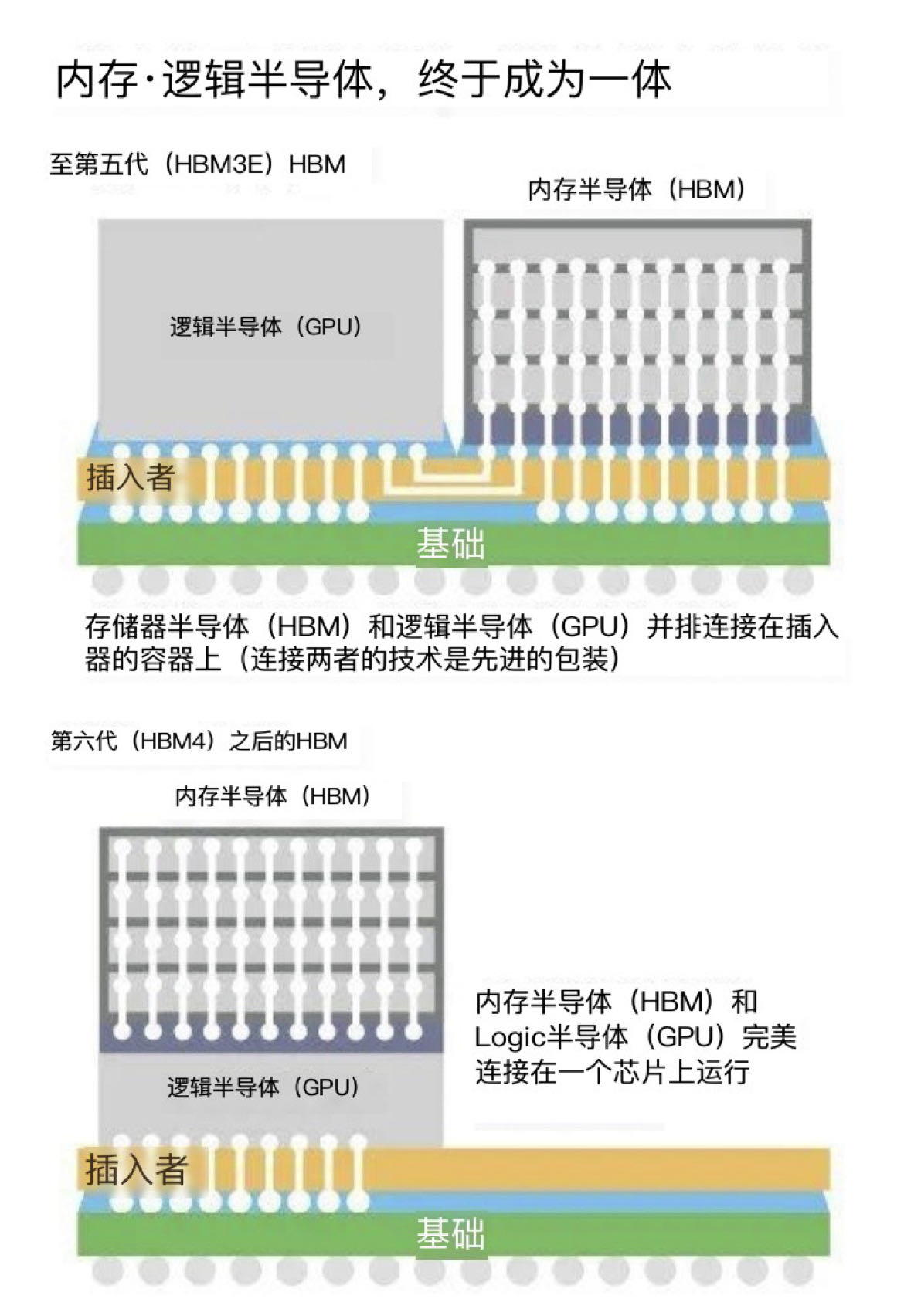

据 Joongang.co.kr 报道,SK海力士已开始招聘CPU和GPU等逻辑半导体的设计人员。该公司显然希望将HBM4直接堆叠在处理器上,这不仅会改变逻辑和存储设备通常的互连方式,而且还会改变它们的制造方式。事实上,如果SK海力士成功,这可能会在很大程度上改变晶圆代工行业的运作方式。

如今,HBM 堆栈集成了 12 个、16 个或 1024 个存储设备,以及一个像集线器一样的逻辑层。HBM 堆栈放置在 CPU 或 GPU 旁边的转接板上,并使用 4 位接口连接到其处理器。SK海力士的目标是将HBM3堆栈直接安装在处理器上,完全消除中介层。在某种程度上,这种方法类似于AMD的<>D V-Cache,它直接放置在CPU芯片上,但HBM当然具有更高的容量,并且更便宜(尽管速度较慢)。

据报道,SK海力士正在与包括英伟达在内的几家无晶圆厂公司讨论其HBM4集成设计方法。SK海力士和英伟达很可能会从一开始就共同设计芯片,并在台积电生产,台积电还将使用晶圆键合技术将SK海力士的HBM4器件放在逻辑芯片上。为了让存储器和逻辑半导体在同一芯片上作为一个主体工作,联合设计是不可避免的。

HBM4 内存将使用 2048 位接口连接到主机处理器,因此 HBM4 的中介层将非常复杂且昂贵。这使得存储器和逻辑的直接连接在经济上可行。但是,虽然将 HBM4 堆栈直接放置在逻辑芯片上会在一定程度上简化芯片设计并降低成本,但这带来了另一个挑战:散热。

(图片来源:翻译自Joongang.co.kr)

现代逻辑处理器,如英伟达的H100,消耗数百瓦的功率,耗散数百瓦的热能。HBM 内存也相当耗电。因此,冷却包含逻辑和存储器的封装可能需要非常复杂的方法,包括液体冷却和/或浸没。

“如果加热问题比现在晚两到三代得到解决,HBM 和 GPU 将能够像一个身体一样在没有中介层的情况下运行,”韩国科学技术院电气和电子系教授 Kim Jung-ho 说。

但是,将内存直接集成在处理器上也将改变芯片的设计和制造方式。使用与逻辑相同的工艺技术在同一晶圆厂上生产 DRAM 将保证最终性能,但会大大增加内存成本,因此这不是现在认真考虑的选择。尽管如此,看起来内存和逻辑已经准备好了,无论是在字面上还是在过程技术层面上。

“在10年内,半导体的'游戏规则'可能会发生变化,存储半导体和逻辑半导体之间的区别可能会变得微不足道,”一位业内人士告诉 Joongang.co.kr。

免责声明:文章来源于tom'shardware,发布/转载只作交流分享,不代表本站的观点和立场。如有异议请及时联系,谢谢。

微信扫一扫,一键转发